|

|||

|

|

|||

|

Page Title:

Table 5-2. Input Display Data Word |

|

||

| ||||||||||

|

|

TM 32-5811-024-14&P

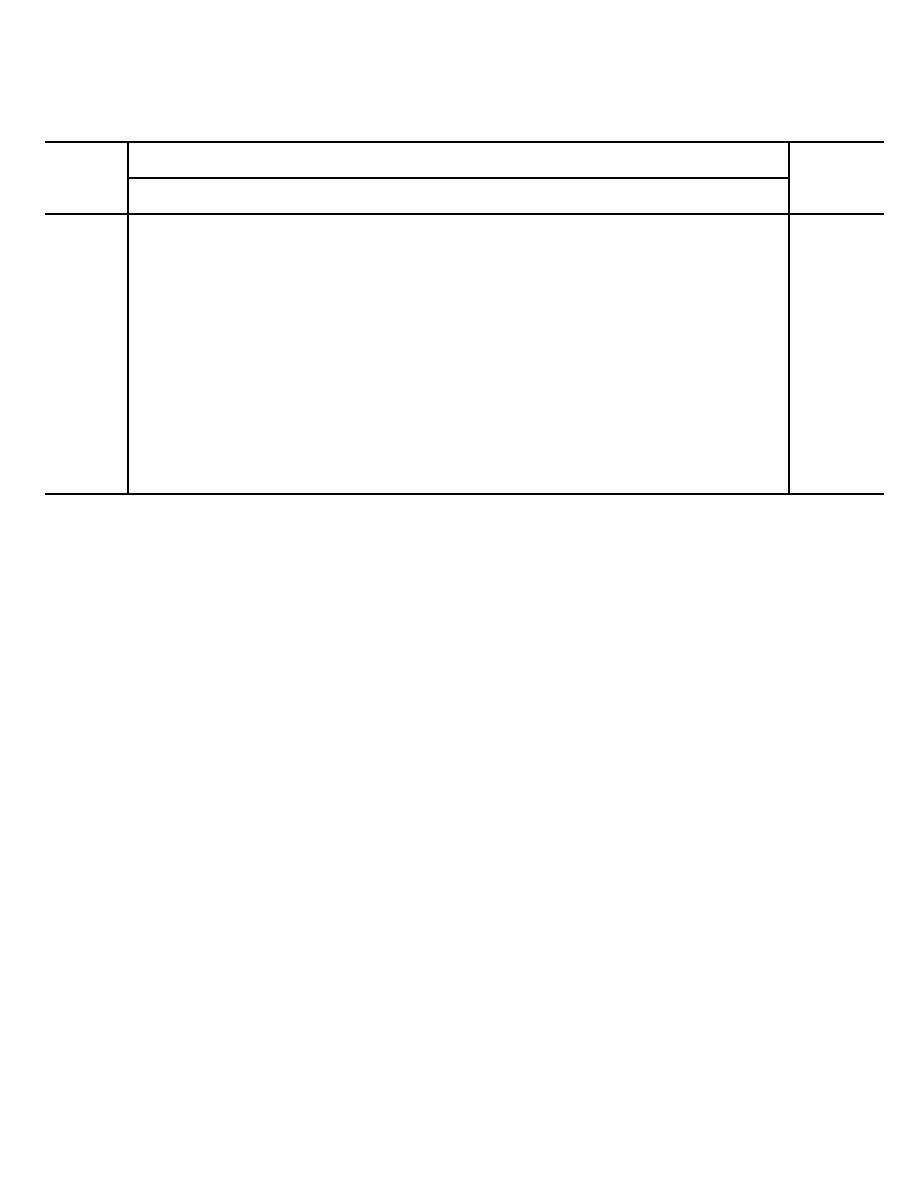

Table 5-2. Input Display Data Word

Display

1

Selected

Data word contents

storage

data

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DMO

latch used

word

(CCA A3)

0

S7

S6

S5

S4

S3

S2

S1

SO

1

S15

S14

S13

S12

S11

S10

S9

S8

2

D7

D6

D5

D4

D3

D2

D1

DO

3

D15

D14

D13

D12

D11

D10

D9

D8

4

INB7

INB6

INB5

INB4

INB3

INB2

INB1

INB0

U14,U15

5

INB15

INB14

INB13

INB12

INB11

INB10

INB9

INB8

U11,U12

6

INB23

INB22

INB21

INB20

INBl9

INB18

INB17

INB16

U9, U10

7

Not

Not

Not

Not

OVFL

CARRY

RUN

F15

U8

used

used

used

used

1

S0-S15

=

Negative true source bus data bits

D0-D15

=

Negative true destination bus data bits

INB0-INB23

=

Positive true instruction bus

(unit under test program ROM output)

OVFL

=

OVERFLOW REGISTER BIT

CARRY

=

CARRY REGISTER BIT

0 = REGISTER CLEAR

Negative

True

RUN

=

DIGITAL PROCESSOR RUNNING

1 = RUNNING 0 = HALTED

F15

=

FLAG 15 (FAULT FLAG)

1 = FLAG SET: FAULT

0 = FLAG CLEAR: NO FAULT

5-8

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |