|

|||

|

|

|||

|

Page Title:

Input-Output Data Rate Compare Function-CONT. |

|

||

| ||||||||||

|

|

T.O. 31W-2GSC24-2

TM 11-5805-688-14-1

NAVELEX 0967-LP-545-3011

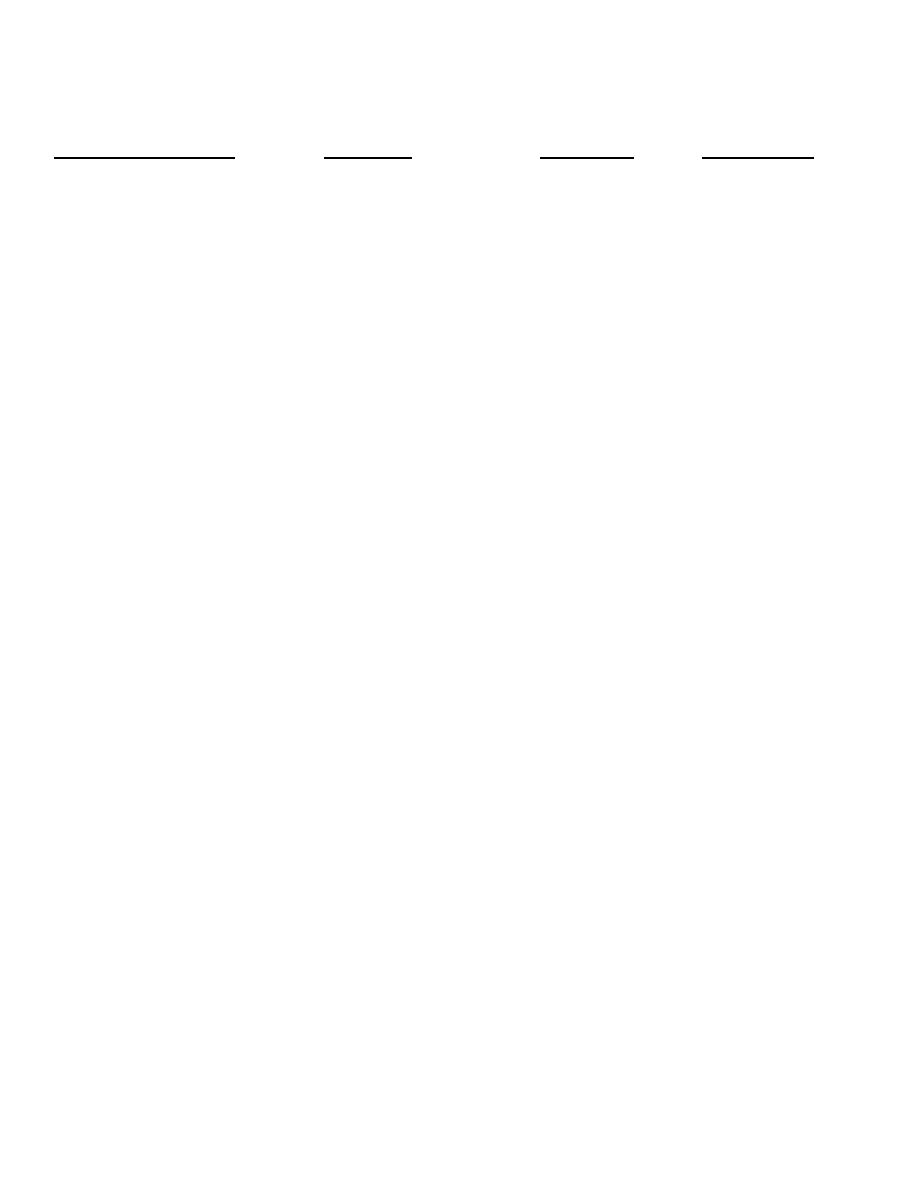

Adder U33 Output

Negative Stuff

Out of Tolerance

E1

E2

E3

E4

Positive Stuff

0

0

0

0

H

L

L

1

0

0

0

H

L

L

Positive

0

1

0

0

H

Stuff

L

L

1

1

0

0

H

L

L

0

0

1

0

H

L

L

1

0

1

0

H*

H*

L

0

1

1

0

H*

H*

L

1

1

1

0

H*

H*

L

0

0

0

1

L

H

L

1

0

0

1

L

H

L

0

1

0

1

L

H

Negative

L

Stuff

1

1

0

1

L

H

L

0

0

1

1

L

H

L

1

0

1

1

H

H

H

0

1

1

1

H

H

H

OOT

1

1

1

1

H

H

H

_______

* No action

out-of-tolerance signal OOT from U31-10 is applied

input is applied to the J input of flip-flop U2-7 when word

through inverter U46-10 to OR gate U47-8 and to J-K

24 signal MW24NXand end-of-scan signal MEOS3NX

flip-flop U49-7. The low-level output from OR gate U47-8

occur at the same time and minor frame terminal count

is applied as a reset signal to the initialization logic. J-K

signal MMF31Xis applied through inverter U53-10 to U2-

flip-flop U49-7, in turn, triggers one-shot multivibrator

10. When the next signal MEOS3NX occurs, the Q

U44 into conduction to generate a low-level out-of-

output from flip-flop U2-7 goes low and presets the

tolerance signal from OR gate U31-4.

outputs of word counter U1, U28, and U15 to zero.

When the next signal MEOS3NX occurs, the Q output

5-l98. Coarse Rate Conversion Circuits. Flip-flop U2-10

from U2-7 goes high and enables the

in the word counter preset control toggles and a high

5-48

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |