|

|||

|

|

|||

|

Page Title:

Table 5-2. Typical Channel Address Input to R.A.M. (Cont.) |

|

||

| ||||||||||

|

|

T.O. 31W2-2GSC24-2

TM 11-5805-688-14-1

NAVELEX 0967-LP-545-3010

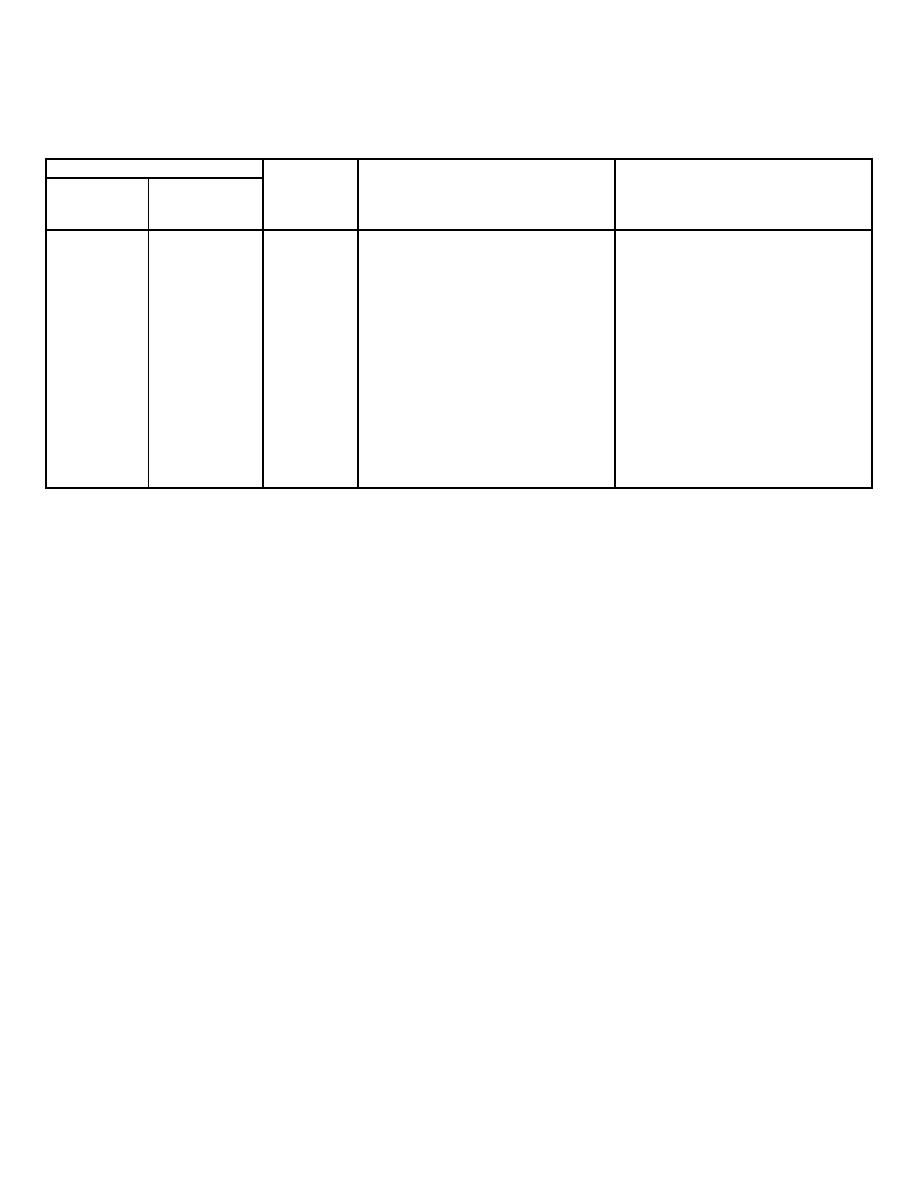

Table 5-2. Typical Channel Address Input to R.A.M. (Cont.)

Ports in Use = 22

Scan

Write

Active (A) /

Counter

Port Address Counter /

Active Channel

Port No.

Strapped (S)

Output

R.A.M. Word Addressed

Address to R.A.M.

24

Don't care

1

22

9

25

since only

26

the ports

27

that are

28

in use are

29

interrogated.

30

31

5-bit write port address (PS1, PS2, PS4, PS8, and PS16)

when the multiplexer set is powered on and when an

applied through the read/write port address selector.

error signal is applied to OR gate U47A as described in

The read/write port address selector, in turn, applies the

the diagnostic function.

write port address to the R.A.M. when a write address

enable from the write/read control is applied to it. The

5-278. Three levels of end-of-scan signals (EOS,

write port address counter is incremented by MRIO and

EOS1, and EOS2) are generated from the end-of-scan

continues to count until it is reset by EOS1 from the end-

register each time an A=B signal is applied to it. Signal

of-scan register. When the counter is reset, the last

EOS1 occurs one RIO clock time after each end of scan,

count should be the 5-bit binary count for the maximum

and EOS2 occurs one clock time after EOS1 occurs.

number of active ports.

Note that DEOS resets the port scan counter to a count

of 1 and EOS1 resets the write port address counter to a

5-277. The write/read control generates the write enable

count of 0. The result is a two- RIO-clock delay between

to the R.A.M. and the write address enable signal to the

the two counters. The delay is required to recover a two-

read/write port address selector when an error signal is

RIO-clock delay related to the logic implementation.

generated from OR gate U47A. The write enable

Signal EOS1 presets the active channel counter to zero

condition lasts for one complete scan cycle (MEOS2 to

and causes the maximum 4-bit channel address from the

MEOS2). The controller generates an inhibit signal to

active channel counter to be loaded into the maximum

AND gate U39 for one scan cycle during every other

channel used register.

scan. In normal operation, a write condition should occur

5-69

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |